注意事項

- Agilex サーバーは試験的な暫定運用です。

- 使用前の予約は不要ですが、他の人と利用がバッティングする可能性もあります。

- Agilex 用の BSP および Quartus など一式の開発環境は ACRi ルーム内でのみ利用可能です。サーバにログインした時点で同意していただいたものとみなします。

Agilex サーバ概要

Agilex サーバでは oneAPI を使った FPGA アクセラレータの開発と DE10-Agilex カードの利用が出来ます。 DE10-Agilex の詳細は terasICのページ を参照してください。

| ホスト名 | CPU | スレッド | メモリ | OS | 搭載FPGA |

|---|---|---|---|---|---|

| iserv1 | Core i7-11700K | 16 | 64GB | Ubuntu 20.04 | Intel® Agilex™ AGFB014R24B2E2V |

Agilex サーバ利用方法

iserv1 には ssh でログインできます。試験的な暫定運用中は予約は不要です。

$ ssh iserv1ログインしたら、環境設定を読み込みます。

$ source /opt/intel/oneapi/setvars.shこれで aocl や oneapi-cli などの oneAPI 開発用のコマンドを利用できます。

$ aocl diagnoseoneAPI のビルドには時間がかかります。途中で ssh セッションが切れる場合などに備えて、 screen や tmuxなどを利用することをおすすめします。

サンプルのビルドと実行

ACRi ルームでは、次の手順で oneAPI のサンプルをビルドして実行することができます。

サンプルプロジェクトの展開

oneAPI のサンプル一式は https://github.com/oneapi-src/oneAPI-samples/tags から取得できます。一式を取得して ACRi ルームのホームディレクトリに展開してください。 ダウンロード済のアーカイブを iserv1 上に置いていますので、以下のコマンドで展開して利用することもできます。

$ tar zxvf /opt/ACRi/oneAPI-stable.tar.gz

$ cd oneAPI-samples-2022.3.0ここで展開される oneAPI-samples-2022.3.0 の 2022.3.0 の部分はバージョンによって異なります。

一式にはたくさんのプロジェクトが含まれていますが、ここでは vector-add のビルドを行ないます。

$ cd ./DirectProgramming/DPC++/DenseLinearAlgebra/vector-addls すると以下のようなファイルを確認することができます。

License.txt build.sh sample.json

Makefile build_fpga.sh src

Makefile.fpga build_fpga_emu.sh third-party-programs.txt

Makefile.win run.sh vector-add-buffers.vcxproj

Makefile.win.fpga run_fpga.sh vector-add-usm.sln

README.md run_fpga_emu.sh vector-add.slnMakefileの書き換え

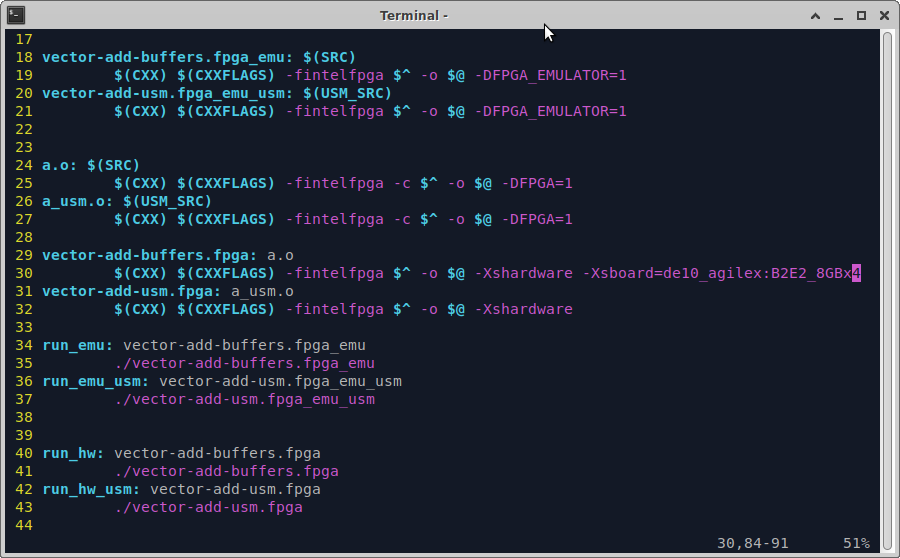

利用する DE10-Agilex 向けにサンプルの Makefile.fpga を編集します。30行目にある vector-add-buffers.fpga ターゲットに対応するコマンドの -Xshardware に続いて、

-Xsboard=de10_agilex:B2E2_8GBx4を追加します。

ビルド

Makefile.fpga を編集したら make コマンドでビルドします。

$ make -f Makefile.fpga hwビルドがはじまると以下のようなメッセージがコンパイルステップに応じてターミナルに出力されます。several hours とか書かれていますが、ビルド完了までには3時間ほどかかります。

dpcpp -O2 -g -std=c++17 -fintelfpga -c src/vector-add-buffers.cpp -o a.o -DFPGA=1

dpcpp -O2 -g -std=c++17 -fintelfpga a.o -o vector-add-buffers.fpga -Xshardware -Xsboard=de10_agilex:B2E2_8GBx4

aoc: Compiling for FPGA. This process may take several hours to complete. Prior to performing this compile, be sure to check the reports to ensure the design will meet your performance targets. If the reports indicate performance targets are not being met, code edits may be required. Please refer to the oneAPI FPGA Optimization Guide for information on performance tuning applications for FPGAs.以下のようなメッセージが表示されてコマンドが終了するとビルド完了です。

'quartus_compile_report.log' and '/tmp/a-f2d191-9c3f49/quartus_compile_report.log' are identical (not copied) at /opt/intel/oneapi/compiler/2022.0.2/linux/lib/oclfpga/share/lib/perl/acl/aoc.pl line 1578.実行

ビルドが終わったら実行しましょう。実行にも Makefile.fpga に定義されているターゲットを利用します。

$ make -f Makefile.fpga run_hw以下のように出力されればサンプルの実行は成功です。

./vector-add-buffers.fpga

Running on device: B2E2_8GBx4 : Agilex Reference Platform (aclde10_agilex0)

Vector size: 10000

[0]: 0 + 0 = 0

[1]: 1 + 1 = 2

[2]: 2 + 2 = 4

...

[9999]: 9999 + 9999 = 19998

Vector add successfully completed on device.このサンプルでは、FPGA 上に構成された

h.parallel_for(num_items, [=](auto i) { sum[i] = a[i] + b[i]; });に相当する回路で入力データの足し算を行ない、その結果をサーバ上で計算した結果と確認しています。